|

ЭНЦИКЛОПЕДИЯ РАДИОЭЛЕКТРОНИКИ И ЭЛЕКТРОТЕХНИКИ Современные ПЛИС фирмы XILINX: серия VIRTEX. Справочные данные

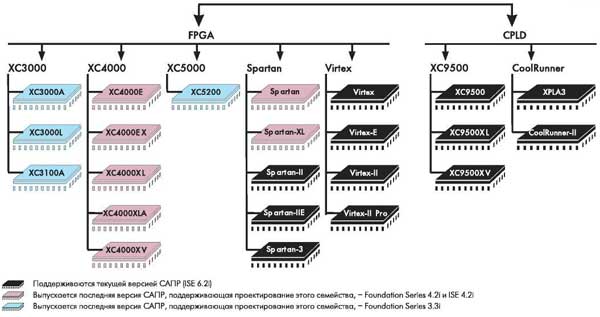

Энциклопедия радиоэлектроники и электротехники / Применение микросхем В 2014 году американская фирма Xilinx отмечает 30-летний юбилей. Уже на раннем этапе своего существования, в 1984 году, компания предложила новый тип логических микросхем - перепрограммируемые пользователем базовые матричные кристаллы (Field Programmable Gate Array, или FPGA). Микросхемы предоставили разработчику электронных устройств преимущества стандартных базовых матричных кристаллов и позволили при этом проектировать, конфигурировать, отлаживать, исправлять ошибки, а также реконфигурировать микросхему непосредственно на рабочем месте. В результате улучшилась гибкость устройства и значительно сократилось время его выхода на рынок готовой продукции. Каковы же достижения компании Xilinx на сегодняшний день? Введение Сегодня компания Xilinx выпускает несколько серий ПЛис. Они подразделяются на FPGA - перепрограммируемые пользователем базовые матричные кристаллы - и CPLD (Complex Programmable Logic Devices) - сложные программируемые логические устройства. В каждой серии - от одного до нескольких семейств, содержащих, в свою очередь, микросхемы, различающиеся емкостью, быстродействием, типом корпусов (см. рисунок). Основные особенности ПЛИС фирмы Xilinx (по состоянию на начало 2004 года): • значительный объем ресурсов: более 10 млн. системных вентилей на кристалл;

Компания Xilinx выпускает ПЛИС на основе трех типов памяти: • СОЗУ (FPGA-типа). При этом конфигурация схемы хранится во внутреннем, "теневом", ОЗУ, а инициализация осуществляется из внешнего массива памяти. Конфигурационная последовательность (bitstream) может быть загружена в FPGA непосредственно в системе и перегружена неограниченное число раз. Инициализация ПЛИС производится автоматически из внешнего загрузочного ПЗУ при подаче напряжения питания или принудительно по специальному сигналу. Процесс инициализации занимает 20-200 мс, в течение которых выводы ПЛИС находятся в высокоомном состоянии (подтянуты к логической единице). К ПЛИС этого типа относятся микросхемы серий Virtex, Spartan;

На этапе отладки конфигурация может загружаться с компьютера с помощью кабелей трех видов: MultiPRO Desktop Tool, Parallel Cable IV и MultiLinx Cable. Все кабели поддерживают программирование микросхем CPLD no JTAG-порту. При выборе кабеля необходимо учитывать их свойства, приводимые ниже: MultiPRO Desktop Tool подключается к параллельному порту ПК, поддерживает внутрисистемное программирование/конфигурирование всех ПЛИС Xilinx, а также автономное программирование ПЛИС семейства CoolRunner-ll и ППЗУ серий XC18V00 и PlatformFlash. При этом наличие в одном комплекте как самого программатора, так и загрузочного кабеля позволило снизить стоимость комплекта средств для отладки и программирования; Parallel Cable IV подключается к параллельному порту ПК, поддерживает загрузку FPGA и программирование CPLD, а также обратное считывание конфигурации через JTAG-порт. Напряжение питания подается от внешнего 5-В источника. В поставку кабеля включен переходник, предназначенный для подачи напряжения питания на кабель от PS/2 порта компьютера; MultiLinx Cable подключается к порту RS-232 ПК или рабочей станции, а также к USB-порту ПК. Напряжение питания (5; 3,3; 2,5 В) подается с платы.

Xilinx предлагает полный набор программного обеспечения, позволяющего реализовать проект на базе выпускаемых ПЛис. Программное обеспечение включает в себя схемотехнический и текстовый ввод, VHDL/Verilog синтез, функциональное моделирование, трассировщик кристаллов, моделирование после трассировки и многое другое. Кроме того, фирма Xilinx разрабатывает специализированные модули, так называемые логические ядра, которые могут быть использованы как библиотечные элементы при проектировании устройств на базе ПЛис. Краткая классификация современных микросхем фирмы XILINX На сегодняшний день наиболее перспективны следующие ПЛИС фирмы Xilinx: • FPGA серии Virtex;

Применение в новых разработках других выпускаемых сейчас серий ПЛИС фирмы Xilinx не рекомендуется. Поэтому их рассматривать не будем. Серия VIRTEX В состав FPGA-микросхем серии входят четыре семейства: Virtex, Virtex-E, Virtex-ll и Virtex-ll Pro. Выпущенные в конце 1998 года микросхемы серии Virtex позволили расширить традиционные свойства ПЛИС FPGA-типа за счет мощного набора свойств, позволяющих решать проблемы проектирования высокопроизводительных систем. FPGA-микросхемы серии характеризуются гибкой архитектурой, состоящей из матрицы конфигурируемых логических блоков (Configurable Logic Blocks - CLB), окруженных программируемыми блоками ввода-вывода (Input-Output Blocks - ЮВ). Специальная логика ускоренного переноса для выполнения высокоскоростных арифметических операций, специальная поддержка умножителей, каскадируемые цепочки для функций с большим числом входов, многочисленные регистры/защелки с разрешением тактирования и синхронным/асинхронным сбросом и установкой, внутренние шины с тремя состояниями обеспечивают баланс быстродействия и плотности упаковки логики. Иерархическая система элементов памяти микросхем серии включает: распределенную память на базе четырехвходовых таблиц преобразования (4-LUT - Look-Up Table), конфигурируемых либо как 16-бит ОЗУ, либо как 16-бит сдвиговый регистр; встроенную блочную память (каждый блок конфигурируется как синхронное двухпортовое ОЗУ) и интерфейсы к модулям внешней памяти. ПЛИС серии поддерживают большинство стандартов ввода-вывода (технология SelectIO™), a FPGA более поздних семейств - стандарты дифференциальной передачи сигналов - LVDS (Low-Voltage Differential Signaling), BLVDS (Bus LVDS), LVPECL (Low-Voltage Positive Emitter-Coupled Logic). Предусмотрены быстродействующие встроенные цепи управления синхронизацией. Проектирование осуществляется работающим на ПК или рабочей станции пакетом программного обеспечения ISE (Integrated Software Environment): ISE BaseX, ISE Foundation, ISE Alliance. Производятся микросхемы серии Virtex с топологическими нормами 0,22-0,15 мкм и многослойной металлизацией. Все микросхемы серии проходят 100%-ное заводское тестирование. Рассмотрим подробнее основные семейства микросхем, входящих в серию Virtex. Семейство Virtex - четвертое поколение FPGA-микросхем после выпуска в 1984 году первой ПЛИС этого типа. FPGA-микросхемы семейства впервые позволили реализовать не только обычные логические функции, но и операции, выполняемые до сих пор отдельными специализированными изделиями. Благодаря появлению семейства Virtex FPGA-микросхемы перешли из разряда связующих логических схем в разряд программируемых устройств, служащих центром цифровых систем. Главные особенности ПЛИС семейства Virtex: высокая производительность (до 200 МГц), большая логическая емкость (50 тыс.-1 млн. системных вентилей), напряжение питания ядра 2,5 В, совместимость с шиной PCI 66 МГц, поддержка функции "горячей замены" для Compact PCI (табл.1). Микросхемы семейства поддерживают 16 высокопроизводительных стандартов ввода-вывода, в том числе LVTTL, LVCMOS2, PCI33, PCI66, GTL/GTL+, SSTL, HSTL, AGP и СТТ, а также прямое подключение KZBTRAM-устройствам. Встроенные цепи управления синхронизацией содержат четыре встроенных модуля автоподстройки задержек (DLL-Delay-Locked Loop) и четыре глобальные сети распределения тактовых сигналов с малыми разбегами фронтов плюс 24 локальные тактовые сети. Каждый блок встроенной памяти конфигурируется как синхронное двухпортовое 4-Кбит ОЗУ (максимальная суммарная емкость 128 Кбит). Таблица 1. Параметры микросхем семейства Virtex

Изготавливаются микросхемы семейства по 0,22-мкм КМОП-техноло-гии с пятислойной металлизацией. Семейство Virtex-E, выпущенное уже в сентябре 1999 года, по своим характеристикам и свойствам сопоставимо со специализированными ASIC. FPGA-микросхемы семейства предназначены для систем обмена данными и цифровой обработки сигнала. В сравнении с микросхемами первого семейства они характеризуются более высокой производительностью (системная частота до 320 МГц) и большей логической емкостью (свыше 2 млн. системных вентилей, табл.2). Подобно предыдущему семейству, технология SelectIO™ обеспечивает поддержку многочисленных стандартов ввода-вывода, в том числе впервые и стандартов дифференциальной передачи - LVDS, BLVDS, LVPECL. Микросхемы семейства поддерживают 32/64-бит, 33/66-МГц PCI. Напряжение питания ядра 1,8 В. Иерархическая трехуровневая система памяти по структуре та же, что и в предыдущем семействе. Но максимальная емкость блочной памяти увеличена в 8,75 раз - до 1120 кбит. Предусмотрены также быстрые интерфейсы к таким внешним высокопроизводительным ОЗУ, как 200-МГц ZBTSRAM и 200-Мбит/с DDR SDRAM.

Таким образом, в микросхемах этого семейства, в сравнении с Virtex, увеличены: • эквивалентная логическая емкость (в три раза);

Таблица 2. Параметры микросхем семейства Virtex-E

Многие высокопроизводительные сетевые системы и системы обработки изображения требуют ОЗУ большого объема. В ответ на это фирма Xilinx в начале 2000 года выпустила версию семейства Virtex-E с увеличенным объемом памяти - Virtex-EM (XCV504E и XCV812E). Таблица 3. Параметры микросхем с увеличенным объемом блочной памяти семейства Virtex-EM

Эти микросхемы - эффективная и надежная платформа для построения коммутационных систем со скоростью передачи 160 Гбит/с (табл.3). Высокая пропускная способность достигнута за счет увеличения объема двухпортовой блочной памяти до 1 Мбит и применения в шестислойной металлизации двух слоев (верхнего и распределения тактовых сигналов), выполненных по медной технологии. Семейство Virtex-ll реализует новую идеологию формирования FPGA-платформ, позволяющую ПЛИС стать основным компонентом цифрового устройства. На одной микросхеме семейства Virtex-ll можно создать сложную цифровую систему логической емкостью до 8 млн. системных вентилей. При этом в сравнении с аналогичной по функциональности заказной интегральной схемой время разработки значительно сокращается. Семейство Virtex-ll включает 11 микросхем, различающихся логической eмкостью (табл.4). Таблица 4. Основные параметры ПЛИС семейства Virtex-ll

Семейство пригодно для проектирования широкого класса высокопроизводительных систем малой и высокой степени интеграции - таких, как устройства передачи данных и устройства цифровой обработки сигналов. На микросхемах семейства Virtex-ll реализуются законченные решения в области телекоммуникационных, сетевых систем, средств беспроводной связи, цифровой обработки сигналов с использованием интерфейсов с PCI, LVDS и DDR. Пример таких решений - реализация процессоров PowerPC 405 и MicroBlaze. Используемая для производства микросхем КМОП-тех-нология c топологическими нормами 0,12-0,15 мкм и восемью слоями металлизации позволяет реализовывать проекты с высоким быстродействием и малым энергопотреблением. Логическая емкость микросхем семейства Virtex-ll составляет 40 тыс.-8 млн. системных вентилей на кристалле, внутренняя тактовая частота - превышает 400 МГц, скорость обмена данными -более 840 Мбит/с по одному контакту ввода-вывода. Объем распределенной памяти достигает 1,5 Мбит, встроенной памяти, реализуемой на блоках двухпортового ОЗУ емкостью 18 кбит каждый, - 3 Мбит. Предусмотрены интерфейсы к внешним модулям памяти типа DDR-SDRAM, QDR™-SRAM и Sigma RAM. Микросхемы семейства содержат блоки умножителей 18x18 бит, до 93184 регистров/защелок с разрешением тактирования и синхронным/асинхронным сбросом и установкой и 93184 функциональных генератора (4-LUT). Управление синхронизацией обеспечивают до 12 модулей управления синхронизацией (DCM) и 16 мультиплексоров глобальных тактовых сигналов. Обеспечивается точная подстройка фронтов тактирующих сигналов, умножение, деление частоты, сдвиг фазы с высоким разрешением и защита от электромагнитных помех. Используемая технология межсоединений Active Interconnect позволяет получать сегментированную структуру трассировки четвертого поколения с прогнозируемыми задержками, не зависящими от коэффициента разветвления по выходу. До 1108 программируемых пользователем блоков ввода-вывода, 19 однополюсных и шесть дифференциальных стандартов ввода-вывода поддерживают большинство цифровых сигнальных стандартов. Встроенные входные и выходные регистры с удвоенной скоростью передачи данных обеспечивают передачу сигналов по стандарту LVDS со скоростью 840 Мбит/с. Программируемая нагрузочная способность по току - 2-24 мА на каждый вывод. Импеданс каждого блока ввода-вывода программируется. Микросхемы Virtex-ll совместимы с шинами PCI-133/66/33 МГц. Возможны пять режимов загрузки конфигурации. Шифрование конфигурационной последовательности осуществляется по стандарту TRIPLE DES, поддержка конфигурирования - по стандарту IEEE 1532. Возможно частичное реконфигурирование. Напряжение питания ядра кристалла равно 1,5 В, блоков ввода-вывода - 1,5-3,3 В в зависимости от запрограммированного сигнального стандарта. Изготавливаются микросхемы по КМОП-технологии с проектными нормами 0,15 мкм (длина канала быстродействующих транзисторов - 0,12 мкм) и восемью слоями металлизации. Семейство Virtex-ll Pro предназначено для создания систем на основе интеллектуальных IP-ядер и заказных параметризируе-мых модулей. Микросхемы семейства оптимизированы под реализацию законченных решений в области телекоммуникаций, беспроводной связи, построения сетей, средств видео- и цифровой обработки сигналов. В архитектуре микросхем впервые предусмотрены многобитовые приемопередатчики RocketIO и процессорные ядра PowerPC. Изготавливаются они по КМОП-технологии с топологическими нормами 0,13 мкм и девятислойной медной металлизацией, позволившей уменьшить размеры кристалла и энергопотребление по сравнению с микросхемами предыдущих серий. Таблица 5. Основные параметры ПЛИС семейства Virtex-ll Pro

Архитектура матриц Virtex-ll и Virtex-ll Pro одинакова. Совпадает и большинство технических характеристик (табл.5). Отличия микросхем двух семейств заключаются в следующем: • меньшее предельное значение напряжения питания периферии: 2,5 В против 3,3 В для серии Virtex-ll;

Серия Virtex-ll Pro - первое семейство ПЛИС с FPGA-архитектурой, в которой реализованы встроенные приемопередатчики RocketIO и процессорные ядра PPC405. RocketIO представляет собой полностью дуплексный последовательный приемопередатчик (SERDES), поддерживающий соединения от 2 до 24 каналов с пропускной способностью от 622 Мбит/с до 3,125 Гбит/с. Скорость двунаправленной передачи данных -120 Гбайт/c. В каждом канале возможен режим внутренней петли обратной связи. Приемопередатчик располагает такими средствами, как встроенная схема формирования и восстановления тактовых сигналов (CDR), возможность выравнивания частоты путем введения/удаления символов, программируемое выделение запятой, 8-, 16- или 32-бит внутренний интерфейс, 8-/10-бит кодер и декодер. RocketIO совместим с протоколами передач Fibre Channel, Gigabit Ethernet, 10 Gb Attachment Unit Interface (XAUI) и широкополосными приемопередатчиками. Конфигурируемые пользователем значения внутреннего согласующего сопротивления приемника/передатчика составляют 50/75 Ом. Предусмотрены пять уровней выходного дифференциального напряжения, четыре уровня установки предыскажений по выбору. Напряжение питания приемопередатчика 2,5 В. Процессорный блок PowerPC представляет собой встроенное ядро на тактовую частоту до 400 МГц с гарвардской архитектурой, пятикаскадным конвейерным трактом передачи данных, аппаратными средствами умножения/деления. Блок также содержит тридцать два 32-разрядных регистра общего назначения, ассоциативные двунаправленные схемы кэш-памяти команд и данных емкостью 16 Кбит каждая, блок управления памятью, 64-входовые буферы трансляции/просмотра (TLB - Translation Look aside Buffers), интерфейс встроенной специальной памяти. Размеры страницы могут изменяться в пределах от 1К до 16 Мбит. Имеется встроенный таймер. Процессорный блок поддерживает шинную архитектуру IBM CoreConnect, операции отладки и трассировки. Его энергопотребление мало: 0,9 мВт/MГц. ПЛИС с FPGA-архитектурой серии Virtex, созданные на основе перспективной промышленной технологии, отличающиеся высокой производительностью и экономической эффективностью, - один из основных типов программируемых логических микросхем, используемых разработчиками всего мира. А с момента их выпуска, в марте 2002 года, фирма Xilinx отгрузила более 100 тыс. ядер PowerPC на основе FPGA-микросхем семейства Virtex-ll Pro. Автор: М. Кузелин; Публикация: cxem.net

Власть является ключевым фактором счастья в отношениях

11.03.2026 Защищенная колонка-повербанк Anker Soundcore Boom Go 3i

11.03.2026 Раннее воздержание от алкоголя перестраивает мозг и иммунитет

10.03.2026

▪ Tesla выпустит электромобиль-амфибию ▪ Электронные сигареты увеличивают риск инсульта ▪ PHILIPS обновил линейку ЖК-телевизоров

▪ раздел сайта Электродвигатели. Подборка статей ▪ статья Семь футов под килем. Крылатое выражение ▪ статья Что происходит, когда вы чувствуете головокружение? Подробный ответ ▪ статья Водитель автолесовоза. Типовая инструкция по охране труда ▪ статья Прохождение сигареты сквозь монету. Секрет фокуса

Главная страница | Библиотека | Статьи | Карта сайта | Отзывы о сайте www.diagram.com.ua | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Оставьте свой комментарий к этой статье:

Оставьте свой комментарий к этой статье: