Бесплатная техническая библиотека

Бесплатная техническая библиотека

Декодеры звуковых сигналов формата MPEG 2.5 LAYER

III STA013/013B/013T. Справочные данные

Энциклопедия радиоэлектроники и электротехники / Применение микросхем

Комментарии к статье

Комментарии к статье

Общие сведения

Микросхема STA013 представляет собой полностью интегрированный универсальный декодер потоков MPEG Layer III Audio спецификаций MPEG 1, MPEG 2 и MPEG 2.5. Приведем основные функции микросхемы: Полная поддержка следующих форматов сжатого звукового сигнала:

- Layer III в стандартах ISO/IEC 11172-3 (MPEG 1 Audio) и ISO/IEC 13818-3.2 (MPEG 2 Audio);

- потоков с низкой частотой дискретизации, известных как MPEG 2.5;

- потоков Layer III в режимах "Стерео", "Два канала", "Один канал" (моно).

Кроме того, микросхема обеспечивает и имеет:

- поддержку всех стандартных частот дискретизации для MPEG 1 и MPEG 2 плюс расширенный набор частот для MPEG 2.5: 48; 44,1; 32; 24; 22,05; 16; 12; 11,025 и 8 кГц ;

- поддержку потока MPEG 2.5 Layer III со скоростями кодирования от 8 до 320 кбит/с;

- программное управление коммутацией каналов в выходном сигнале;

- цифровое управление уровнем выходного сигнала;

- цифровое управление уровнем низких и высоких частот в выходном сигнале (регулировка тембра);

- работу последовательного интерфейса для данных;

- поддержку программно-управляемого формата данных для выходного последовательного интерфейса (PCM);

- низкое энергопотребление (85 мВт при питающем напряжении 2,4 В и максимальной частоте дискретизации сигнала);

- проверку целостности входных данных (CRC) и обнаружение ошибок синхронизации входного потока с возможностью регистрации этих ошибок внешним контроллером.

Управление микросхемой осуществляется по шине I2C.

К микросхеме могут быть подключены внешние кварцевые резонаторы с частотами 10, 14,31818 и 14,7456 МГц (возможна поддержка и других частот, но для этого потребуется соответствующая версия внутреннего программного обеспечения (firmware). Основная сфера применения микросхемы - аудиотехника с поддержкой формата MP3: CD-плееры, MP3-плееры, музыкальные центры. Низкое напряжение питания и малое потребление энергии делает эту микросхему особенно удобной для применения в переносимых и портативных аппаратах. Также микросхема может применяться в компьютерных звуковых картах для воспроизведения звука в формате MP3 без участия центрального процессора. Основные характеристики микросхемы приведены в табл. 1.

Таблица 1

| Характеристики |

Значение |

| Напряжение питания микросхемы,В |

2,1…3,6 |

| Рассеиваемая мощность,мВт:\при частоте дискретизации 24кГц \32кГц \48кГц |

\76\79\85 |

| Рабочий интервал температур, oC |

-20…+125 |

| Диапазон регулирования уровня выходного сигнала,дБ |

-96…0 |

| Шаг регулировки уровня выходного сигнала,дБ |

1 |

| Диапазон регулировки уровня высоких частот,дБ |

-18…+18 |

| Диапазон регулировки уровня низких частот,дБ |

-18…+18 |

| Шаг регулирования уровня частот (высоких и низких),дБ |

1,5 |

| Длительность сигнала сброса (RESET), мкС |

не менее 0,1 |

Основные подсистемы микросхемы STA013

Структурная схема микросхемы приведена рис. 1. Входной последовательный интерфейс служит для приема потока входных данных от внешнего источника. Порядок передачи битов - старший бит передаваемых байтов передается первым. Данные принимаются по входу SDI и синхронизируются по изменению уровня сигнала на входе SCKR. Настройка синхронизации (прием данных по фронту или спаду импульса) осуществляется программно. Низкий уровень на входе BIT_EN запрещает прием данных входным интерфейсом.

Рис. 1. Структурная схема микросхемы

Синтезатор частот и модуль синхронизации служат для генерации тактовых сигналов для вычислительного ядра микросхемы и для выходного аудиоинтерфейса. Частоты дискретизации выходного сигнала получаются делением частоты передискретизации OCLK на программно заданный коэффициент. Синтезатор частот может генерировать выходные сигналы для управления большинством из распространенных микросхем ЦАП.

Выходной последовательный интерфейс служит для вывода декодированных звуковых данных в формате PCM. Данные передаются по линии SDO и синхронизированы тактовым сигналом на выходе SCKT. Настройка синхронизации (передача данных по фронту или спаду импульса) осуществляется программно. Уровень сигнала на выходе LRCKT указывает канал (левый/правый), для которого передается слово данных. Точность представления сигнала может быть выбрана программно из четырех значений: 16, 18, 20 или 24 бита. При выборе точности представления 16 бит за один период сигнала LRCKT передается 32 бита данных. Если же выбрана точность представления 18, 20 или 24 бита, то за один период сигнала LRCKT передаются 64 бита данных. Формат передаваемых данных управляется программно, что позволяет подключить к микросхеме множество различных типов внешних ЦАП, поддерживающих последовательный протокол передачи данных.

Интерфейс I2C служит для управления режимами работы микросхемы посредством внешнего микроконтроллера, а также для получения информации о текущем состоянии модулей микросхемы. Все регулировочные параметры микросхемы записаны во внутренние регистры и доступны для записи по шине I2C. Вычислительное ядро микросхемы представляет собой высокопроизводительный цифровой сигнальный процессор (DSP), обеспечивающий декодирование звукового потока формата MP3, цифровую фильтрацию сигнала, а также управление модулем синхронизации микросхемы.

Режимы работы микросхемы

Микросхема STA013 может работать в двух режимах - Multimedia Mode (MM) или Broadcast Mode (далее BM). В режиме MM входным потоком данных управляет сама микросхема STA013 посредством изменения уровня сигнала на выходе DATA_REQ. Активный сигнал на этом выходе указывает внешнему источнику на необходимость передавать данные микросхеме STA013. При работе в этом режиме вывод SRC_INT должен быть соединен с источником питания. В режиме BM входным потоком данных полностью управляет источник данных. В случае несовпадения реальной скорости потока входных данных и заданной номинальной скорости микросхема STA013 обеспечивает необходимую внутреннюю синхронизацию автоматически. Режим BM в основном требуется для работы микросхемы в носимых или портативных устройствах.

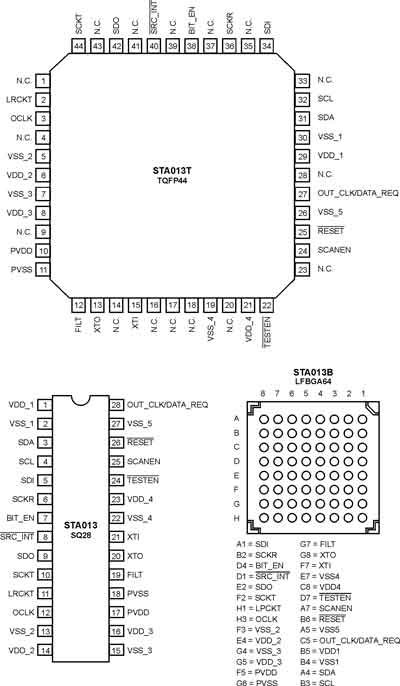

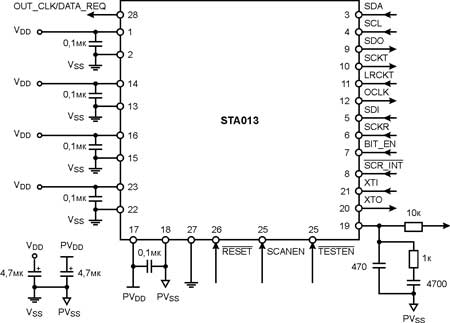

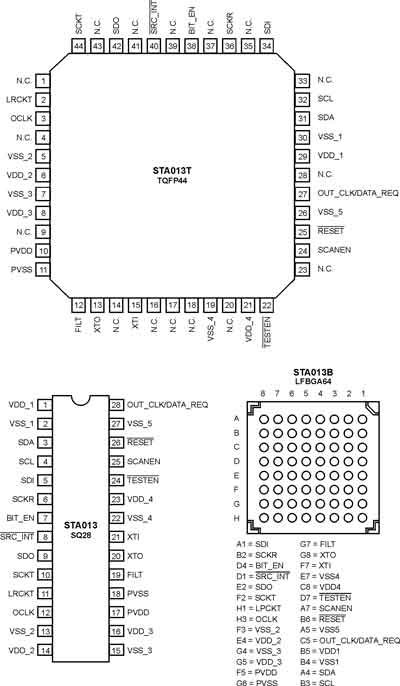

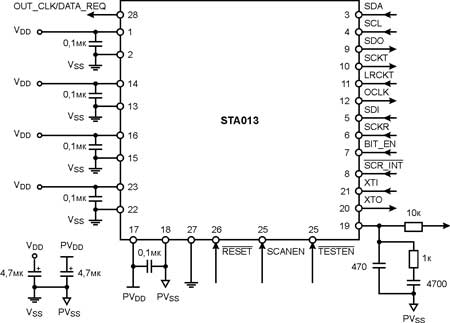

Цоколевка микросхемы для каждого из вариантов исполнения приведена на рис. 2, а схема включения - на рис. 3 и 4.

Рис. 2. Цоколевка микросхемы

Рис. 3. Схема включения

Рис. 4. Схема включения

Назначение выводов микросхемы STA013 приведено в табл. 2.

Таблица 2

| Номер вывода |

Обозначение |

Описание |

| Корпус SO8 |

Корпус TQFP44 |

Корпус LBGA64 |

| 1 |

29 |

B5 |

VDD_1 |

Напряжение питания |

| 2 |

30 |

B4 |

VSS_1 |

Общий провод |

| 3 |

31 |

A4 |

SDA |

Вход/выход. Линия данных шины I2C |

| 4 |

32 |

B3 |

SCL |

Вход. Тактовый сигнал шины I2C |

| 5 |

34 |

A1 |

SDI |

Вход. Линия данных входного последовательного интерфейса |

| 6 |

36 |

B2 |

SCKR |

Вход. Тактовый сигнал входного последовательного интерфейса |

| 7 |

38 |

D4 |

BIT_EN |

Вход. Сигнал достоверности входных данных |

| 8 |

40 |

D1 |

SRC_INT |

Вход. Сигнал прерывания от источника входных данных |

| 9 |

42 |

E2 |

SDO |

Выход. Линия данных выходного последовательного интерфейса (декодированные данные в формате PCM) |

| 10 |

44 |

F2 |

SCKT |

Выход. Тактовый сигнал выходного последовательного интерфейса |

| 11 |

2 |

H1 |

LRCKT |

Выход. Тактовый сигнал данных канала (левый/правый) |

| 12 |

3 |

H3 |

OCLK |

Вход/выход. Тактовый сигнал передискретизации для внешнего ЦАП |

| 13 |

5 |

F3 |

VSS_2 |

Общий провод |

| 14 |

6 |

E4 |

VDD_2 |

Напряжение питания |

| 15 |

7 |

G4 |

VSS_3 |

Общий провод |

| 16 |

8 |

G5 |

VDD_3 |

Напряжение питания |

| 17 |

10 |

F5 |

PVDD |

Напряжение питания синтезатора частот |

| 18 |

11 |

G6 |

PVSS |

Общий провод синтезатора частот |

| 19 |

12 |

G7 |

FILT |

Выход. Фильтр выходного синхросигнала |

| 20 |

13 |

G8 |

XTO |

Выход. Подключение кварцевого резонатора |

| 21 |

15 |

F7 |

XTI |

Вход. Подключение кварцевого резонатора |

| 22 |

19 |

E7 |

VSS_4 |

Общий провод |

| 23 |

21 |

C8 |

VDD_4 |

Напряжение питания |

| 24 |

22 |

D7 |

TESTEN |

Вход. Включение тестового режима |

| 25 |

24 |

A7 |

SCANEN |

Вход |

| 26 |

25 |

B6 |

RESET |

Вход. Сигнал аппаратного сброса |

| 27 |

26 |

A5 |

VSS_5 |

Общий провод |

| 28 |

27 |

C5 |

OUT_CLK/DATA_REQ |

Тактовый сигнал выходного буфера/Сигнал запроса данных |

Автор: Владимир Зайцев; Публикация: cxem.net

Смотрите другие статьи раздела Применение микросхем.

Смотрите другие статьи раздела Применение микросхем.

Читайте и пишите полезные комментарии к этой статье.

Читайте и пишите полезные комментарии к этой статье.

<< Назад

Последние новости науки и техники, новинки электроники:

Последние новости науки и техники, новинки электроники:

Власть является ключевым фактором счастья в отношениях

11.03.2026

Исследования семейных и романтических отношений показывают, что длительное счастье пары зависит не только от привычных факторов, таких как доверие, уважение и преданность, но и от более тонких психологических аспектов. Современные ученые ищут закономерности, которые отличают действительно счастливые пары от остальных, чтобы понять, какие механизмы поддерживают гармонию в отношениях.

Группа исследователей из Университета Мартина Лютера в Галле-Виттенберге и Бамбергского университета провела опрос среди 181 пары, которые состояли в совместных отношениях более восьми лет и прожили вместе хотя бы месяц. Участники заполняли анкету, описывая различные аспекты своих отношений, включая распределение обязанностей, эмоциональную поддержку и степень вовлеченности в совместные решения.

Анализ данных показал интересный паттерн: пары, где оба партнера ощущали высокий уровень личной власти, оказывались наиболее счастливыми и удовлетворенными. В данном контексте под властью понимается способност ...>>

Защищенная колонка-повербанк Anker Soundcore Boom Go 3i

11.03.2026

Компания Anker представила новую модель линейки Soundcore - колонку Soundcore Boom Go 3i, ориентированную на активное использование на улице.

Новинка отличается высокой степенью защиты: корпус соответствует стандарту IP68, что обеспечивает водо- и пыленепроницаемость, а ударопрочный дизайн выдерживает падение с высоты до одного метра. За качество звука отвечает 15-ваттный драйвер, обеспечивающий пик громкости до 92 дБ, а технология BassUp 2.0 усиливает низкие частоты, делая звучание более насыщенным.

Колонка обладает автономностью до 24 часов, а LED-индикатор позволяет контролировать уровень заряда батареи. Кроме того, Soundcore Boom Go 3i может выполнять функцию павербанка: согласно внутренним тестам, устройство способно зарядить iPhone 17 с нуля до 40% за один час, что делает его полезным аксессуаром в походах и поездках.

Среди функциональных особенностей модели стоит выделить технологию Auracast, которая улучшает подключение и позволяет создавать стереопару из двух колонок ...>>

Раннее воздержание от алкоголя перестраивает мозг и иммунитет

10.03.2026

Алкогольная зависимость - хроническое расстройство с компульсивным употреблением спиртного, которое влияет не только на поведение, но и на функционирование мозга и иммунной системы. Недавние исследования показали, что даже на ранних этапах воздержания организм начинает перестраиваться, открывая новые возможности для терапии зависимости.

Ученые сосредоточились на пациентах, находящихся в первые недели абстиненции, и зафиксировали значительные изменения в мозговой активности. С помощью функциональной магнитно-резонансной томографии они выявили перестройку сетей нейронных связей, отвечающих за контроль импульсов и принятие решений. Эти изменения могут быть ключевыми для восстановления самоконтроля и снижения риска рецидива.

Одновременно с нейронной перестройкой исследователи наблюдали колебания иммунной системы. В крови повышался уровень цитокинов - сигнальных белков, регулирующих воспалительные процессы. Эти данные свидетельствуют о существовании нейроиммунного взаимодействия, при ...>>

Случайная новость из Архива Случайная новость из Архива Накопители данных большой емкости

31.03.2000

Канадские ученые разработали новый ферромагнитный материал, из которого можно будет изготовлять накопители данных большой емкости. На основе полимеров и железа была получена ферромагнитная керамика.

При нагревании этого материала атомы железа приходят в движение и начинают мигрировать, сливаясь и образуя так называемые нанокластеры. Чем крупнее кластеры, тем сильнее магнетизм материала.

Таким образом, магнитные свойства материала можно в определенных пределах регулировать.

|

Другие интересные новости:

Другие интересные новости:

▪ Мини-компьютеры Gigabyte Brix

▪ Поддержка DisplayPort в разъеме USB Type-C

▪ Акустические маяки защитят от столкновения с птицами

▪ Смарт-жилетка Carhartt X-1

▪ Длинные пальцы депрессии

Лента новостей науки и техники, новинок электроники

Лента новостей науки и техники, новинок электроники

Интересные материалы Бесплатной технической библиотеки:

Интересные материалы Бесплатной технической библиотеки:

▪ раздел сайта Узлы радиолюбительской техники. Подборка статей

▪ статья Радиационная разведка. Основы безопасной жизнедеятельности

▪ статья Каким был первый банк? Подробный ответ

▪ статья Камелия эвгенольная. Легенды, выращивание, способы применения

▪ статья Экономичное управление симистором. Энциклопедия радиоэлектроники и электротехники

▪ статья Хитрые булавки. Секрет фокуса

Оставьте свой комментарий к этой статье:

Оставьте свой комментарий к этой статье:

Главная страница | Библиотека | Статьи | Карта сайта | Отзывы о сайте

www.diagram.com.ua

2000-2026

Оставьте свой комментарий к этой статье:

Оставьте свой комментарий к этой статье: