|

ЭНЦИКЛОПЕДИЯ РАДИОЭЛЕКТРОНИКИ И ЭЛЕКТРОТЕХНИКИ Микроконтроллеры 8ХС51СВ фирмы INTEL. Энциклопедия радиоэлектроники и электротехники

Энциклопедия радиоэлектроники и электротехники / Микроконтроллеры В состав группы 8XC51GB входят микроконтроллеры 80С51GВ, 83С51GВ, 87С51GВ, 80С51GВ-1, 83С51GВ-1 и 87С51GВ-1. На момент подготовки статьи все они выпускались в 68-выводном корпусе РLСС и маркировались с префиксом N (N80С51GВ, N83C51GВ и т. д.). Кристаллы выполнены по СНМОS III-Е технологии фириы Intel. Версии с программируемым внутренним ПЗУ не имеют прозрачного окна в корпусе, т. е. относятся к разряду однократно программируемых. Это несколько ограничивает круг их потребителей в силу того, что при отладке не удается работать методом проб и ошибок с многократным перепрограммированием кристалла, а обязательно приходится использовать соответствующий эмулятор. Первые три из названных выше контроллеров работают при частоте тактового сигнала от 3,5 до 12 МГц, остальные работоспособны в интервале частот 3,5...16 МГц. Напряжение питания всех контроллеров - 5 В, низковольтные версии не выпускались. Основные технические характеристики контроллеров группы 8хС51GВ:

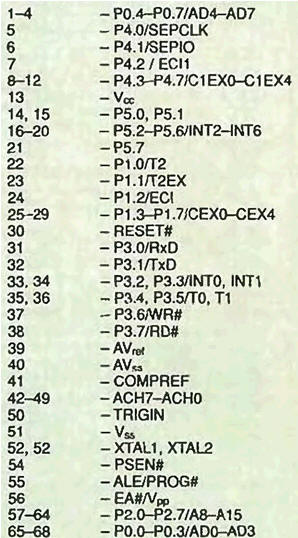

Большинство из названных характеристик присущи всему семейству МСS51, в связи с чем мы не будем подробно на них останавливаться. Тем, кто не знаком с ними, рекомендуем обратиться к статьям об однокристальных микро-ЭВМ, опубликованным в [1-3]. Кроме того, при анализе микроконтроллеров 8хС51Fх, 8x151Fх [4] был подробно описан массив программируемых счетчиков, в связи с чем он также будет рассмотрен только с точки зрения его отличий от имеющегося в 8хХ51Fх. Предметом нашего знакомства будут те из особенностей 8хС51GВ,которых нет ни у одной из остальных групп семейства МСS51. Отметим,, что контроллеры 80С51GВ и 80С51GВ-1 но содержат внутренней памяти программ, 83С51GВ и 83С51GВ-1 имеют масочно программируемое ПЗУ объемом соответственно 8 и 16 Кбайт, а 87С51GВ и 87С51GВ-1 - перепрограммируемое ПЗУ объемом соответственно 8 и 32 Кбайт. НАЗНАЧЕНИЕ ВЫВОДОВ Назначение выводов контроллеров рассматриваемой группы следующее:

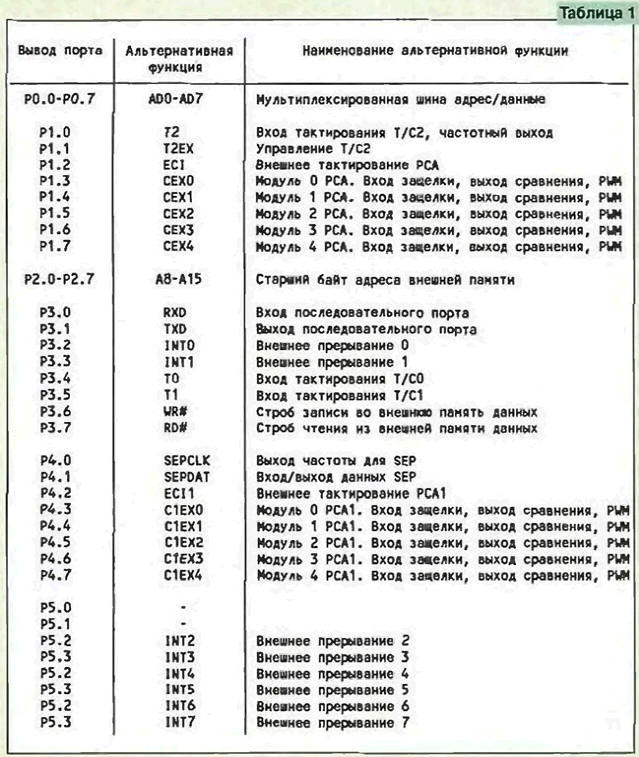

Большинство из названных выводов знакомы тем, кто уже имел дело с микроконтроллерами семейства МСS51. Новыми являются выводы портов Р4, Р5 со своими альтернативными функциями (они приведены после знака /), выводы питания (АVrol, АVss) и сигналов, связанных с АЦП (СОМРREF, АСН0-АСН7, TRIGIN), которые будут рассмотрены при описании соответствующих устройств. Порт РО аналогичен соответствующим портам более ранних микросхем и выполняет те же функции. У контроллеров 8хС51GВ появились два новых порта - Р4 и Р5. Как и Р1-РЗ. они являются восьмибитными квазидвунаправленными портами ввода-вывода с мощным внутренним резистором, обеспечивающим быстрое установление на выходах уровня логической 1 при переключении. Резистор подключается к выходному каскаду на два периода тактового генератора для перевода вывода в указанное состояние, а затем отключается. Выводы портов Р1-Р5, находящиеся в состоянии логической 1, имеют высокий потенциал за счет внутреннего резистора и могут использоваться в этом состоянии как входы. В отличие от РО, входные линии портов Р1-Р5 снабжены триггерами Шмитта. Почти все выводы портов имеют аль тернативное назначение (табл. 1). При сбросе выводы порта РЗ устанавливаются в единичное состояние, остальных - в нулевое. Вход RESET#- сброс. Низкий уровень на этом входе в течение двух машинных циклов при работающем тактовом генераторе приводит к сбросу контроллера. Выводы портов устанавливаются в исходное состояние в момент, когда напряжение на входе RESЕТ# снижается до 0,3...0,4 В. Процедура сброса длится пять машинных циклов (60 периодов тактового генератора). Необходимо обратить внимание на то, что полярность сигналов сброса микроконтроллеров группы 8хС81GВ - обратная по отношению к другим микросхемам семейства МСS51. Причины этой инверсии автору неизвестны. Вход ALE/PROG# полностью аналогичен соответствующему входу других контроллеров семейства МСS51. Отметим, что в 8хС51GВ пользователь имеет возможность запретить выдачу сигнала АLЕ. установив в 0 младший бит из регистра SFR, расположенный по адресу 8ЕН. Сигнал А1Е выдается только в момент действия команды МО\/С или МО\/Х, в остальных случаях на этом выводе удерживается единичный уровень. При работе только с внутренней памятью программ и данных на выходе АLЕ вообще не будет никаких сигналов. Вход ЕА#/Vрр служит для разрешения выборки команд из внутренней памяти программ, если таковая имеется на кристалле и вход соединен с общим проводом. При подаче на него единичного уровня выполняется программа из внешней памяти программ. Однако последнее возможно только до того момента, пока не установлены биты защиты внутренней памяти программ, о чем будет сказано ниже. На этот вывод подают напряжение программирования Vрр = 12,75 В при программировании внутреннего ПЗУ микросхем 87С51GВ, 87С51GВ-1. ОТЛИЧИЯ 8ХС51GВ ОТ ОСТАЛЬНЫХ ИЗДЕЛИЙ СЕМЕЙСТВА МСS51 Итак, перечислим наиболее существенные отличия контроллеров 8хС51GВ. Это:

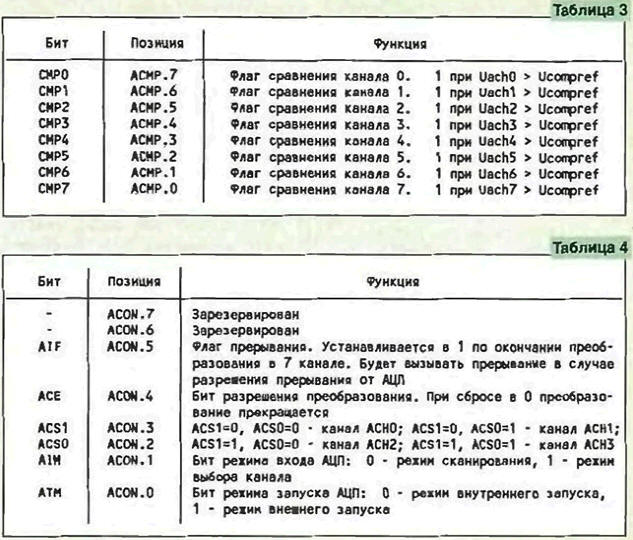

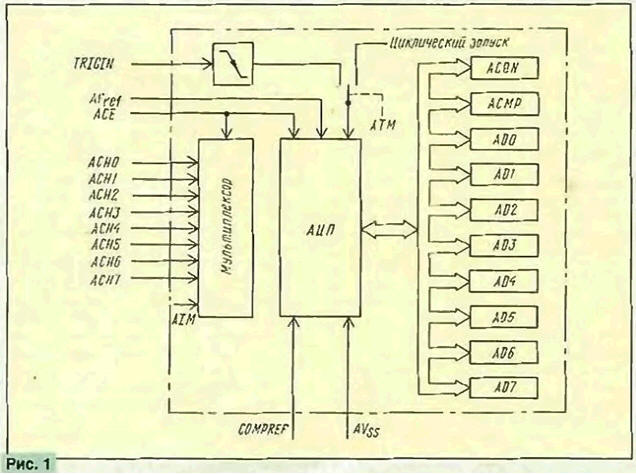

УЗЕЛ АЦП АЦП микроконтроллеров 8хС51GВ (см. функциональную схему на рис. 1) имеет восемь аналоговых входов (выводы AСН0-АСН7), вход внешнего запуска ТRIGIN, выводы питания (АVHrol) и общего провода (АVss) аналоговой части, развязанные гальванически с соответствующими выводами цифровой, а также вывод опорного (образцового) напряжения сравнения СОМРREF. В состав АЦП входят входят восьмиканальный мультиплексор, 256-элементная резистивная линейка, компаратор, устройство выборки/хранения, восемь регистров результата, регистр последовательного приближения и регистр результата сравнения. Фактически в пространстве SFR имеется 10 дополнительных регистров. Регистры АD0-АD7 (84Н,94Н, 0А4Н, 0В4Н, 0С4Н, 0D4Н, 0Е4Н, 0F4Н) содержат результаты преобразования по каждому из восьми каналов. Значение каждого регистра обновляется по завершении преобразования в соответствующем канале, начиная с канала 0. Регистр результатов сравнения АСМР (0С7Н) содержит восемь флагов, отражающих результаты сравнения сигналов на аналоговых входах АСН0-АСН7 с напряжением на входе СОМРREF (табл. 3). Соответствующий флаг устанавливается в 1 в том случае, если входное напряжение на этом аналоговом входе превышает СОМРREF" в противном случае флаг сбрасывается. Регистр АСОМ (097Н) содержит флаг прерывания АЦП АLF, бит разрешения преобразования АСЕ, два бита выбора канала АСSО и АСS1, биты режима входа АIМ и режима запуска АТМ (табл. 4).

РЕЖИМ СРАВНЕНИЯ Этот режим всегда активен и используется для сравнения напряжений на входах АСН0-АСН7 с образцовым напряжением, подаваемым на вход СОМРREF контроллера. При всяком запуске АЦП состояние каждого бита регистра АСМР изменяется на новое, начиная с канала 0, независимо от установленного режима опроса каналов. Режим позволяет быстро осуществить сравнение типа больше-меньше двух аналоговых сигналов аппаратным методом, что может существенно сократить и упростить выполняемую программу. Если режим сравнения не используется, на вход СОМРREF можно подать любое напряжение от Vcc до Vss. РЕЖИМ ЗАПУСКА Запуск АЦП возможен как от внутреннего, так и от внешнего источника. В первом случае бит АТМ регистра АСОN должен быть установлен в 1. В этом режиме в цикле, следующем затем, в котором бит АСЕ был установлен в 1, начинается преобразование с канала 0. После завершения преобразования в седьмом канале устанавливается флаг АLF, Если прерывание от АЦП разрешено, установка флага в 1 вызывает прерывание по вектору АЦП. Новый цикл начинается после завершения предыдущего. Установка бита АСЕ в 0 завершает преобразование, В режиме внешнего запуска преобразование начинается при наличии нулевого уровня на входе TRIGIN. На этом входе нет фиксации перепада, и его состояние определяется путем опроса в каждом машинном цикле. Другими словами, для запуска преобразования длительность сигнала с нулевым уровнем на входе TRIGIN должна быть больше продолжительности машинного цикла. После запуска цикла до его завершения состояние входа TRIGIN игнорируется и преобразование осуществляется так же, как и в предыдущем случае. После завершения цикла АЦП останавливается до прихода на вход TRIGIN нового импульса или до внутреннего запуска битом АСЕ.

РЕЖИМ ВХОДА Установка бита AIM в 0 переводит АЦП в так называемый режим сканирования, в котором преобразование осуществляется в последовательности АСНО, АСН1.....АСН7. Результаты преобразования помещаются соответственно в регистры ADO. AD1.....AD7. При установке бита AIM в 1 после старта АЦП производятся четыре последовательных преобразования сигнала в канале, номер которого определяется состоянием битов ACS0 и ACS1 регистра ACON. Результаты этих измерений сигнала в выбранном канале записываются в регистры AD0-AD3. После этого АЦП. как и в режиме сканирования, опрашивает каналы АСН4-АСН7. результаты преобразования заносятся в AD4-AD7. ИСПОЛЬЗОВАНИЕ АЦП ДЛЯ МЕНЬШЕГО ЧИСЛА КАНАЛОВ

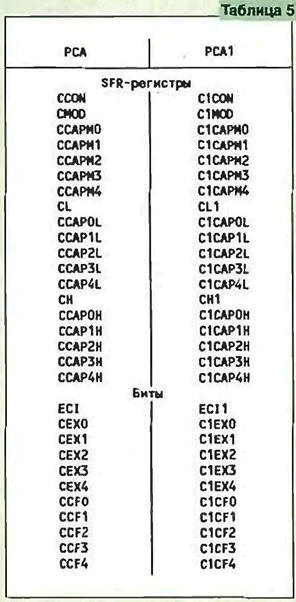

Имеется несколько вариантов использования АЦП с числом каналов, меньшим восьми. Если время преобразования не критично, то можно просто дождаться прерывания после завершения преобразования в седьмом канале и считать результаты только из выбранных каналов. Если же важно получить результат сразу после завершения преобразования в выбранном канале, Intel предлагает отсчитывать нужный временной интервал с использованием таймера и его прерываний. Еще один рекомендуемый способ - периодический опрос состояния соответствующего регистра результата. Его изменение дает информацию о том, что произошло новое преобразование (правда, этот способ годится только в том случае, если измеряемое напряжение непостоянно). Использование режима выбора канала не уменьшает время преобразования, а лишь увеличивает чиспо измерений в выбранном канале за один цикл. АЦП В РЕЖИМЕ МИКРОПОТРЕБЛЕНИЯ В состав АЦП контроллеров 8xC51GB входит цепь, ограничивающая энергопотребление узла в режимах XX и МП до значения тока утечки. Для нормального функционирования этой цепи на вывод AVioi микроконтроллера нужно подать потенциал Усе. В течение времени нахождения АЦП в режиме пониженного потребления напряжение питания можно уменьшать до 2,5 В. МАССИВЫ ПРОГРАММИРУЕМЫХ СЧЕТЧИКОВ В состав микроконтроллера 8xC51GB входит массив программируемых счетчиков (РСА), аналогичный используемому в 8xC51Fx [4]. Однако у 8xC51GB есть еще и второй аналогичный массив - РСА1. Его отличия от РСА заключаются в следующем:

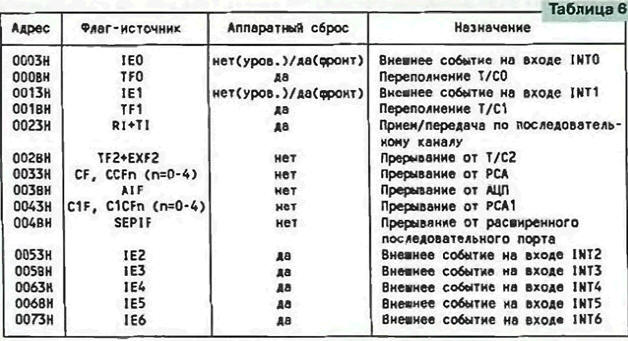

Микроконтроллеры 8хС51GВ поддерживают 15 векторов прерываний (табп. 6). Младшие пять из них аналогичны имеющимся во всех контроллерах семейства МСS51, шестой обслуживает третий таймер/счетчик (он появился только начиная с кристаллов семейства МСS52), седьмой, имеющийся только в 8хС51FX, 8х151FXи8хС51GВ, поддерживает программируемую матрицу счетчиков (РСА). Последний дополнительно располагает прерываниями от пяти внешних входов (INT2 - INT6). второй матрицы программируемых счетчиков, АЦП и расширенного последовательного порта.

Во всех контроллерах семейства МСS51 каждое прерывание может быть запрещено установкой в низкий уровень соответствующего бита в регистре IЕ Естественно, это справедливо и для 8хС51GВ. Однако поскольку он содержит вдвое больше источников прерывания, то для их разрешения/запрещения используется дополнительный регистр IЕА (табл. 7). Как и в предыдущем случае, установка бита в 1 приводит к разрешению соответствующего прерывания, сброс в 0 запрещает его. Адрес регистра IЕА-0А7Н. Отметим, что все прерывания, в том числе и описанные в табл. 7, могут быть одновременно запрещены установкой в 0 бита ЕА (IЕ.7) - старшего бита регистра IЕ.

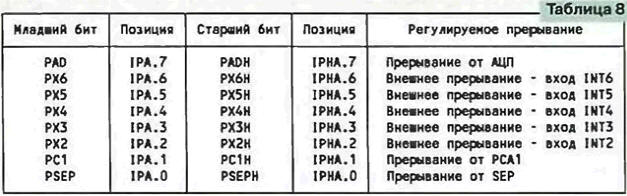

Каждое прерывание может иметь свой собственный приоритет (от уровня 0 - низшего, до уровня 3 - высшего). Уровень приоритета определяется состоянием бит в регистровых парах IР, IРН и IРА, IРНА. Первая из них идентична имеющейся в более ранних контроллерах и подробно описана при рассмотрении группы 8хС51Fх. Вторая пара (адреса регистров соответственно 0В8Н и 0В6Н) имеется только в 8хС51GВ и обслуживает прерывания, которые есть только в этих контроллерах. В табл. 8 показано соответствие между битами регистров и прерываниями, уровень которых они определяют, в табл. 9 - соответствие между уровнями приоритетов и состоянием бит в регистровых парах IР, IРН и IРА, IРНА.

Прерывания с низким приоритетом могут быть, в свою очереди, прерваны только событием более высокого приоритета (но не равного). Соответственно прерывание с высшим приоритетом прервано быть не может. Если процессор одновременно получил запросы на два или более прерываний с одинаковым приоритетом, то очередность их обработки определяется специальной последовательностью опроса флагов прерывания. У контроллеров 8хС51GВ она выглядит следующим образом:

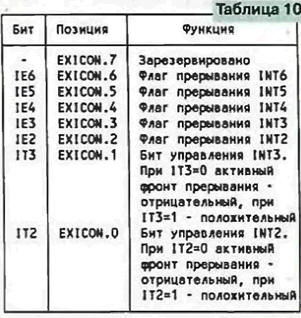

Внешние прерывания I NT0 и INТ1 микроконтроллера 8хС51GВ полностью соответствуют аналогичным прерываниям всех микросхем семейства МСS51 и в зависимости от состояния бит ITО и IT1 регистра ТСОN могуг фиксироваться как по уровню, так и по перепаду из 1 в 0. Внешние выводы INТ2 и INТЗ могут реагировать как на положительный, так и на отрицательный фронт сигнала. Микросхема имеет регистр ЕХIСОN (0С6Н), содержащий биты IT2 и ITЗ, определяющие активный фронт сигнала на выводах Р5.2(INT2) и Р5.3(INTТЗ). При установке бита ITn в 0 прерывание инициируется по отрицательному фронту, при ITn = 1 - по положительному. Внешние события INT4 - INT6 фиксируются только по положительному фронту на выводах P5.4(INT4) - P5.6(INT6). Все внешние прерывания генерируют соответствующие аппаратно устанавливаемые флаги. Для событий INTO, INT1 - это биты 1Е0 и IE1 регистра TCON. Флаги IE2-IE6 находятся в регистре EXICON. Их сброс осуществляется аппаратно в момент перехода процессора на подпрограмму обработки соответствующего прерывания. За время машинного цикла опрос выводов внешних прерываний осуществляется лишь однажды. Поэтому для того чтобы прерывание было зарегистрировано, длительность его активного уровня должна превышать продолжительность одного машинного цикла (12 периодов тактового генератора). Назначение бит регистра EXICON приведено в табл. 10.

РАСШИРЕННЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ Расширенный последовательный порт (SEP) располагает аппаратными средствами для реализации шины 1C-bus, де-факто являющейся стандартом последовательного обмена. SEP допускает функционирование в четырех различных режимах, имеет три различных источника тактирования. Под его нужды задействовано два вывода микросхемы: Р4.1 - ввода/вывода данных и Р4.0 - для вывода тактирующего сигнала. Передаваемый или принимаемый пакет состоит из восьми бит данных. При этом используется восемь тактов работы SEP. В отсутствие принимаемой или передаваемой информации тактовый сигнал и данные неактивны. За SEP закреплены три SFR-регистра: SEPCON (0D7H), SEPDAT (0Е7Н) и SEPSTAT (0F7H). Адресуются они только побайтно. Назначение бит в регистрах SEPCON и SEPSTAT приведено в табл. 11 и 12 соответственно.

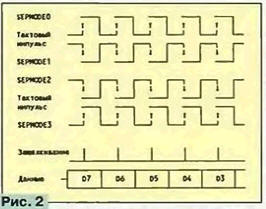

На рис. 2 показаны отличительные особенности режимов работы SEP - активные уровни сигнала тактирования и фронты, используемые для приема или передачи. Как следует из табл. 11, режим работы SEP определяется состоянием бит CLKPOL и CLKPH, расположенных в регистре SEPCON.

Для приема или передачи байта пользователь должен выбрать режим работы порта (биты CLKPOL и CLKPH), скорость передачи (SEPS1 и SEPS0) и установить в 1 бит SEPE Процесс передачи начинается сразу после загрузки байта в регистр SEPDATA. Прием инициируется установкой в 1 бита SEPREN в случае, когда регистр SEPDATA пуст и нет передачи. После приема восьми бит SEPREN аппаратно сбрасывается. Завершение приема или передачи приводит к установке в 1 бита SEPIF. Его сброс возможен только программным путем. Если пользователь предпримет попытку записать информацию в регистр SEPDATA (или прочитать ее из него) в момент передачи или приема, устанавливается соответствующий бит ошибки. Флаг SEPFWR устанавливается при попытке сделать это в процессе передачи байта, a SEPFRD - в процессе приема. Прерывания, связанные с установкой этих бит отсутствуют, вследствие чего пользователь должен контролировать их состояние самостоятельно. Естественно, сброс этих флагов может быть осуществлен только программным путем. АППАРАТНЫЙ СТОРОЖЕВОЙ ТАЙМЕР Аппаратный сторожевой таймер (HWDT) сбрасывает микроконтроллер при своем переполнении, что является средством борьбы с зависанием системы (зацикливанием программы). На выполнение аналогичной функции может быть настроен и таймер/счетчик модуля 4 РСА, но такое его применение ограничивает возможности пользователя, в связи с чем в 8xC51GB появился самостоятельный WDT, не требующий использования РСА. Аппаратный сторожевой таймер состоит из 14-битного счетчика, инкрементируемого в каждом машинном цикле, и SFR-регистра WDTRST (0А6Н). Таймер всегда активен и при работающем тактовом генераторе непрерывно увеличивает содержимое счетчика, Средств остановки таймера нет. Если программа пользователя не записывает в WDTRST никакой информации, то через каждые 16 384 машинных цикла HWDT формирует сигнал RESET, который сбрасывает микроконтроллер. При этом счетчик обнуляется. Для предупреждения срабатывания HWDT пользовательская программа с промежутком не реже 16 383 машинных циклон должна заносить в регистр WDTRST последовательно два байта - 01ЕН и 0А6Н. Отметим, что в WDTRST можно только записывать информацию, средства чтения его содержимого отсутствуют. Не рекомендуется производить упомянутый перезапуск сторожевого таймера с помощью подпрограммы обработки прерывания от одного из таймеров/счетчиков, поскольку прерывания могут обрабатываться и при зависшей основной программе. Лучшее место для расположения команд обнуления сторожевого таймера - циклически выполняемый программный фрагмент, период повторения которого меньше времени срабатывания HWDT.

При переводе 8xC51GB в режим микропотребления внутренний тактовый генератор и HWDT останавливаются. Выведение контроллера из режима микропотребления, как и у всех его предшественников, может быть осуществлено двояко: сбросом или вызовом внешнего прерывания, разрешенного перед переводом 8xC51GB в названный режим. В первом случае обнуляется HWDT, во втором при старте тактового генератора содержимое счетчика HWDT продолжит увеличиваться. Но поскольку для устойчивого запуска тактового генератора необходимо время около двух десятков его периодов, рекомендуется длительность импульса внешнего прерывания, выводящего контроллер из режима микропотребления, делать не меньшей упомянутого времени. Программа обработки прерывания начнет выполняться только после перехода уровня сигнала внешнего прерывания в 1, когда частота генерации стабилизируется. Тогда же и начнется инкрементирование счетчика HWDT, т. е. пока сигнал прерывания имеет нулевой уровень, HWDT не работает. В режиме XX тактовый генератор контроллера не отключается. Вследствие этого содержимое счетчика HWDT непрерывно увеличивается и для предотвращения пересброса необходимо использовать таймерное прерывание, по которому будут осуществляться выход из этого режима, обнуление счетчика сторожевого таймера и возврат в режим Idle. Ниже приводится фрагмент кода, использующего прерывание от Т/СО для периодического сброса HWDT. Правда, как отмечалось выше, использование гакого прерывания - не лучшее место для обнуления счетчика, и подобную процедуру лучше встроить в периодически выполняемую часть программы - опрос клавиатуры или отображение информации. Поэтому приводимый фрагмент следует рассматривать как демонстрационный пример, а не как подпрограмму, которую нужно использовать в программах без каких-либо изменений. ОБНАРУЖЕНИЕ СБОЯ ТАКТОВОГО ГЕНЕРАТОРА Цепь обнаружения сбоя тактового генератора (OFD) предназначена для сброса микроконтроллера, если частота генератора окажется ниже предельного значения, заданного техническими условиями. Если после сброса тактовая частота не изменится (вернее, не возрастет до допустимого значения), контроллер так и останется в этом состоянии. Отметим, что превышение частоты сверх установленной границы не приводит к его сбросу. Цепь OFD всегда включается после сброса или при выходе контроллера из режима микропотребления. Для ее отключения необходимо записать последовательно 0Е1Н и 01ЕН в регистр OSCR (0А5Н). Это необходимо сделать, в частности, перед переходом в режим микропотребления, поскольку в нем тактовый генератор выключен. Разрешить работу цепи заново можно лишь пересбросом или выходом из режима микропотребления по внешнему прерыванию. Состояние цепи OFD может быть определено путем чтения регистра OSCR. При OSCR=0FFH обнаружение сбоев разрешено, при OSCR=0FEH - запрещено, ЗАКЛЮЧЕНИЕ Итак, мы завершили рассмотрение особенностей восьмиразрядных микроконтроллеров семейства MCS51, разработанных и выпускаемых фирмой Intel. Они оказались настолько удачными, что тиражирование многих из них (с некоторыми технологическими усовершенствованиями) продолжается и поныне. Устойчивый спрос на эти контроллеры определяется тем, что сотни тысяч разработчиков привыкли к ним, наработали огромный объем программного обеспечения, обзавелись парком отладочных и кросс-средств. Во многих случаях новая разработка не требует замены микроконтроллера на что-то кардинально новое, в связи с чем целесообразнее выполнить ее на том, что уже знакомо и обеспечено средствами поддержки, а не тратить силы и средства на переход к иной элементной базе. По этой причине Intel регулярно усовершенствовала свои контроллеры, чтобы расширить круг решаемых с их использованием задач. Более того, к подобному усовершенствованию присоединились фирмы, не имевшие отношения к первоначальной разработке. Так, сегодня совместимые с этим семейством микроконтроллеры выпускают фирмы Philips, Siemens, Dallas Semiconductor, Atmel, OKI и некоторые менее известные производители, в том числе и ряд предприятий на территории бывшего СССР. Все контроллеры имеют одинаковые набор команд и базовую архитектуру, как правило, совместимы по "цоколевке" и имеют схожие алгоритмы программирования. Однако есть и существенные различия в наборе дополнительных регистров и аппаратных средств. Так, микроконтроллеры фирмы Dallas Semiconductor имеют два регистра DPTR и механизм их переключения, изделия Philips - АЦП повышенной разрядности, у контроллеров Siemens на кристалле нередко расположена внешняя память, адресуемая командами MOVX, и т. д. Литература

Автор: А.Фрунзе, г.Москва

Власть является ключевым фактором счастья в отношениях

11.03.2026 Защищенная колонка-повербанк Anker Soundcore Boom Go 3i

11.03.2026 Раннее воздержание от алкоголя перестраивает мозг и иммунитет

10.03.2026

▪ Портативные устройства вредят развитию речи ▪ 2D материал толщиной в 1 атом ▪ Аксессуар Biostar для добычи криптовалют ▪ Компьютерный корпус с пылесосом

▪ раздел сайта Медицина. Подборка статей ▪ статья Окно в Европу. Крылатое выражение ▪ статья Тримараны Стриж. Личный транспорт ▪ статья VFO с электронной перестройкой. Энциклопедия радиоэлектроники и электротехники

Главная страница | Библиотека | Статьи | Карта сайта | Отзывы о сайте www.diagram.com.ua |

Оставьте свой комментарий к этой статье:

Оставьте свой комментарий к этой статье: